2024 ICCAD CAD Contest Problem C: Scalable Logic Gate Sizing Using ML Techniques and GPU Acceleration

Authors

B.-Y. Wu, R. Liang, G. Pradipta, A. Agnesina, H. Ren, and V. A. Chhabria

Abstract

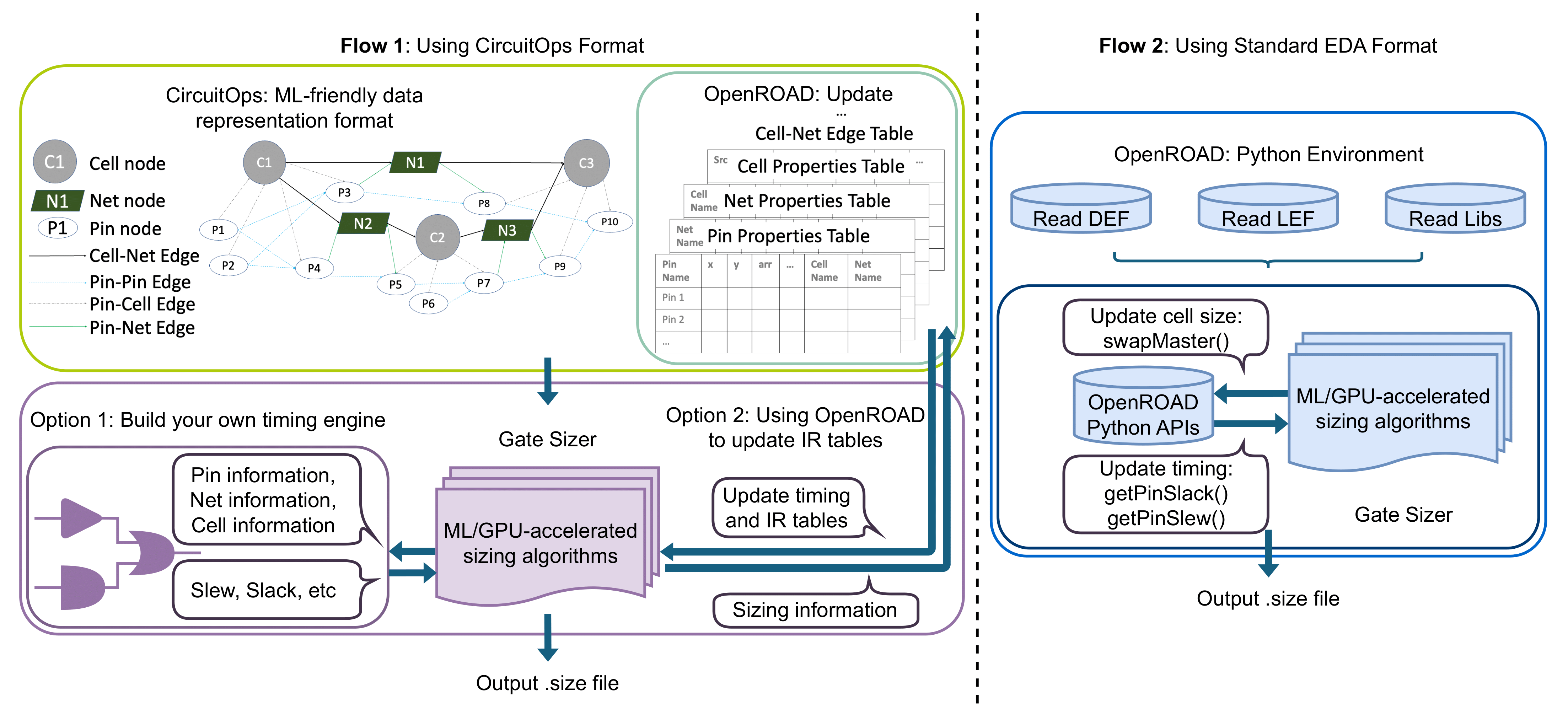

Logic gate sizing plays a vital role in timing optimization, especially as Moore’s Law slows, shifting greater responsibility to EDA tools to enhance power, performance, and area (PPA), as these gains are no longer achieved solely through scaling and process advancements. There is an increasing need to push the limits of logic gate sizing to extract every possible improvement in PPA. With recent breakthroughs in machine learning (ML) and the computational power of GPUs, there is significant potential to elevate logic gate sizing algorithms to new heights. This contest aims to advance logic gate sizing and push the boundaries of PPA improvement through innovative EDA tools that leverage machine learning and GPU acceleration. As part of the contest, an infrastructure has been developed to enable ML and GPU-accelerated logic gate sizing algorithms, including the release of benchmarks in both standard EDA and ML-friendly formats, along with examples of incorporating “ML inside” EDA tools through Python APIs. The contest leverages the open-source EDA tool OpenROAD and ML-friendly data representation format, CircuitOps, to lower barriers to entry by providing accessible formats and tools, allowing participants to build on existing software without redundancy. With over 25 teams actively participating, the contest highlights growing interest and potential to push the boundaries of timing optimization.